ARM<sup>®</sup> Cortex<sup>™</sup>-M0

32-bit microcontroller

2.4G RF transceiver

# HSMicro HS6207™ Series Technical Reference Manual

## Version 1.1

| 1 | 目え   | 录      |                                                                                          |     |

|---|------|--------|------------------------------------------------------------------------------------------|-----|

| 1 | HS62 | 207    |                                                                                          | 4   |

| - | 1.1  |        | Configuration                                                                            |     |

|   | 1.2  |        | Description                                                                              |     |

|   |      | 1.2.1  | I/O Function                                                                             |     |

|   |      |        | Function Description                                                                     |     |

| 2 | MCL  |        |                                                                                          |     |

|   | 2.1  |        | neral Description                                                                        |     |

|   | 2.2  |        | iture                                                                                    |     |

|   | 2.3  |        | ck Diagram                                                                               |     |

|   | 2.4  |        | nctional Description                                                                     |     |

|   |      | 2.4.1  | ARM <sup>®</sup> Cortex™-M0 core                                                         | 10  |

|   |      | 2.4.2  | Memory Map                                                                               |     |

|   |      | 2.4.3  | Watchdog Timer (WDT Base address = 0x4780 0000)                                          |     |

|   |      | 2.4.4  | Timer (Timer0 Base address = 0x4680_0000; Timer1 Base address = 0x4680_0100)             |     |

|   |      | 2.4.5  | Capture/PWM (PWM Base address = 0x4280 0000)                                             |     |

|   |      | 2.4.6  | Universal Asynchronous Receiver/Transmitter (UART) with modem control (UARTO Base a      |     |

|   |      | 0x448  | 0_0000; UART1 Base address = 0x4500_0000; UART2 Base address = 0x4580_0000)              |     |

|   |      | 2.4.7  | Inter-Integrated Circuit (I <sup>2</sup> C) Controller (I2C0 Base address = 0x4800_0000) | 35  |

|   |      | 2.4.8  | Analog-to-Digital Converter (ADC) (ADC Base address = 0x4300_0000)                       |     |

|   |      | 2.4.9  | System Configuration (SYSCON Base address = 0x5000_0000)                                 |     |

|   |      | 2.4.10 | Flash Memory Controller (FMC) (FMC Base address = 0x4980 0000)                           |     |

|   |      |        | General Purpose I/O (GPIO) (GPIO) Base address = 0x5200 0000; GPIO1 Base address =       |     |

|   |      |        | 0 0000; GPIO2 Base address = 0x5300 0000; GPIO3 Base address = 0x5380 0000)              | 64  |

|   |      |        | Nested Vectored Interrupt Controller (NVIC Base address = 0xE000 E000)                   |     |

|   |      |        | System Control Block (SCB Base address = 0xE000_E000)                                    |     |

|   |      |        | System timer (SysTick Base address = 0xE000_E000)                                        |     |

|   |      | 2.4.15 | User Configuration (Base address = 0x1000_0000)                                          |     |

| 3 | RF   |        |                                                                                          | 96  |

|   | 3.1  | Int    | roduction                                                                                | 96  |

|   |      | 3.1.1  | Features                                                                                 | 97  |

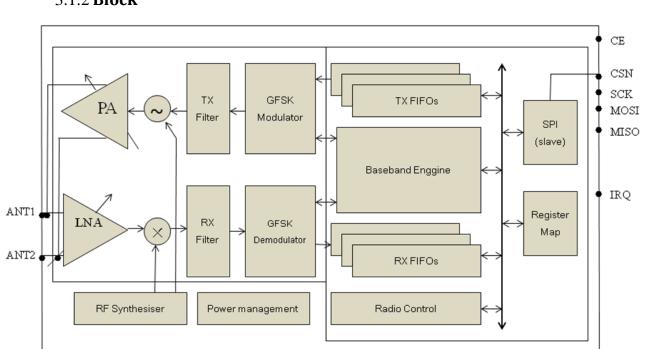

|   |      | 3.1.2  | Block                                                                                    | 98  |

|   | 3.2  | Rad    | dio Control                                                                              | 99  |

|   |      | 3.2.1  | Operational Modes                                                                        | 99  |

|   |      | 3.2.2  | Air data rate                                                                            | 101 |

|   |      | 3.2.3  | RF channel frequency                                                                     | 102 |

|   |      | 3.2.4  | Received Power Detector measurements                                                     | 102 |

|   |      | 3.2.5  | PA control                                                                               | 102 |

|   |      | 3.2.6  | RX/TX control                                                                            | 103 |

|   | 3.3  | Pro    | tocol Engine                                                                             | 103 |

|   |      | 3.3.1  | Features                                                                                 | 103 |

|   |      | 3.3.2  | Protocol engine overview                                                                 |     |

|   |      | 3.3.3  | Protocol engine packet format                                                            |     |

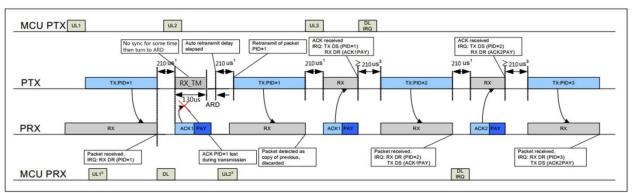

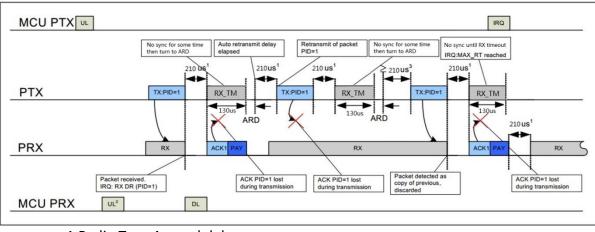

|   |      | 3.3.4  | Automatic packet transaction handling                                                    |     |

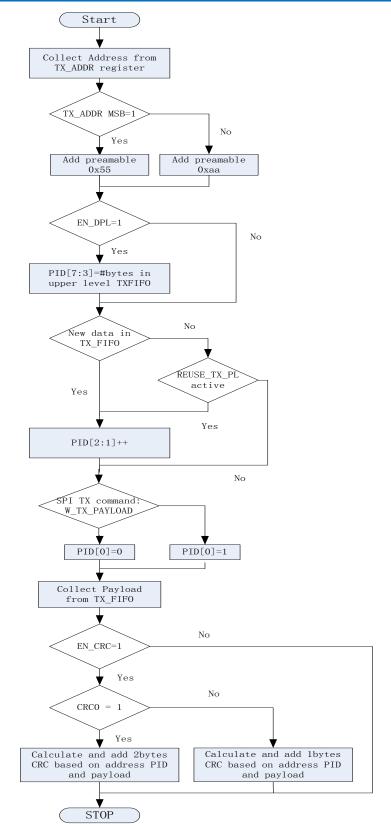

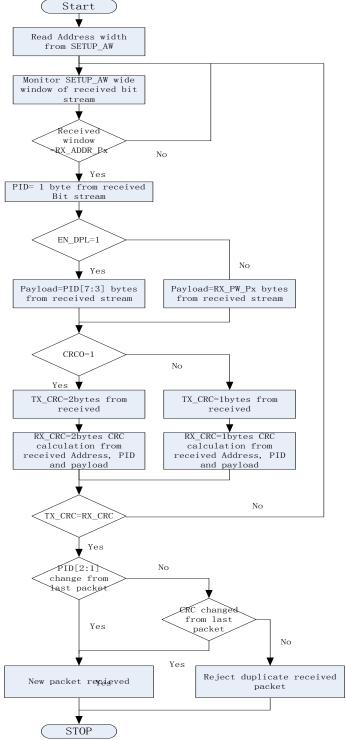

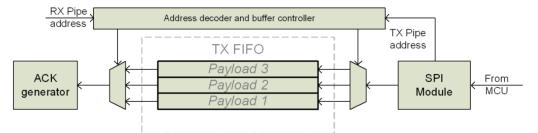

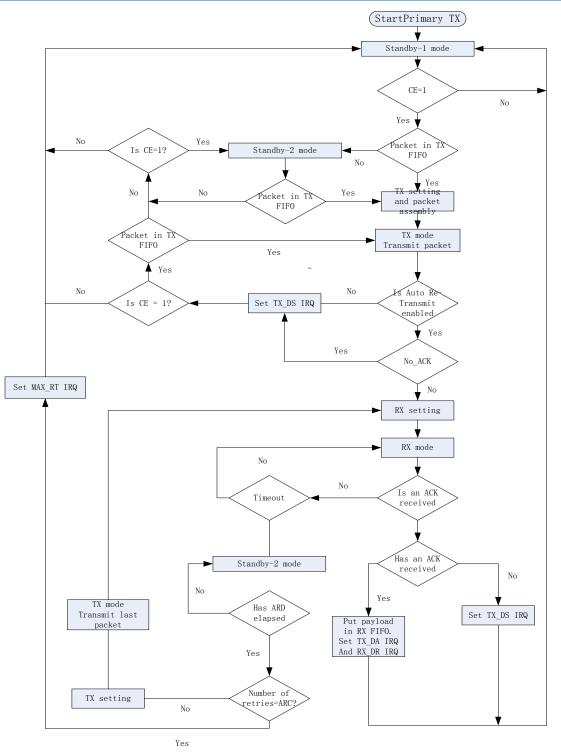

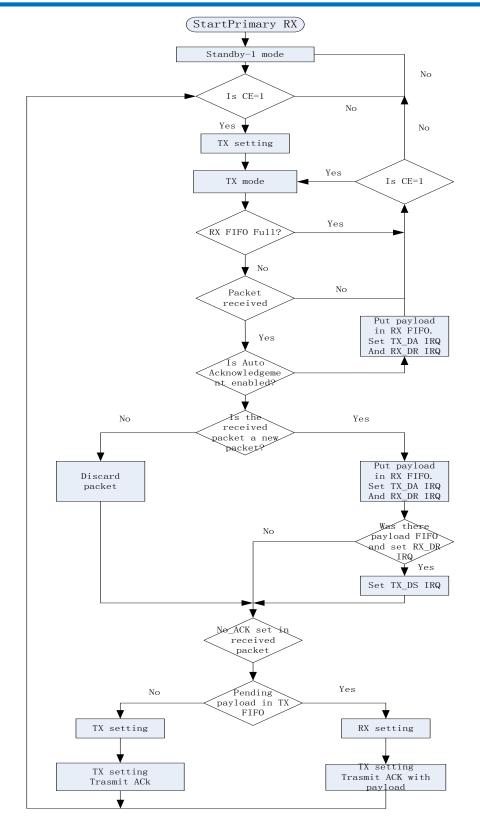

|   |      | 3.3.5  | Protocol engine flowcharts                                                               |     |

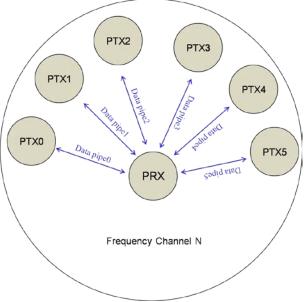

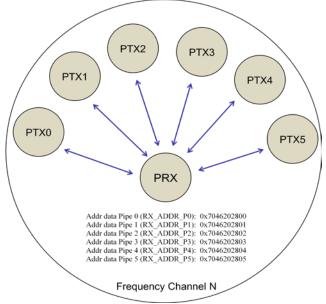

|   |      | 3.3.6  | MultiSlave                                                                               |     |

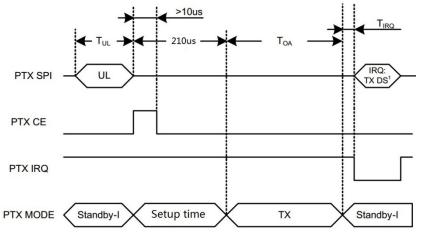

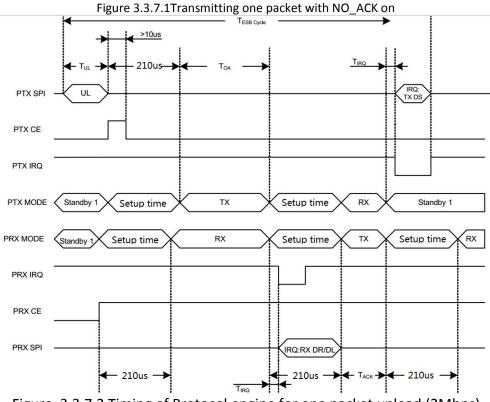

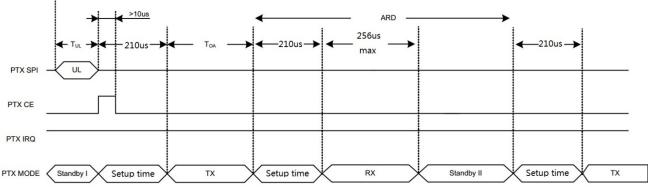

|   |      | 3.3.7  | Protocol engine timing                                                                   |     |

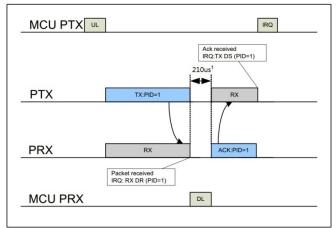

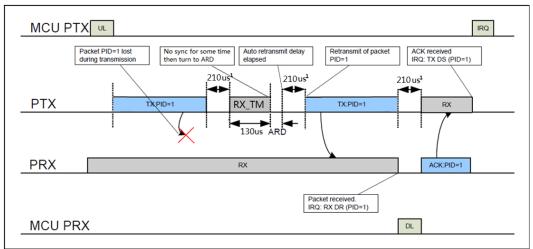

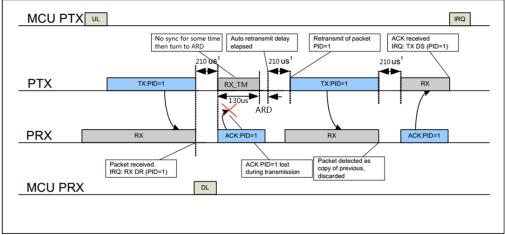

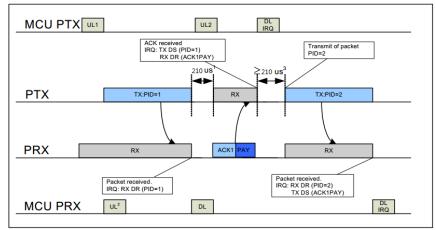

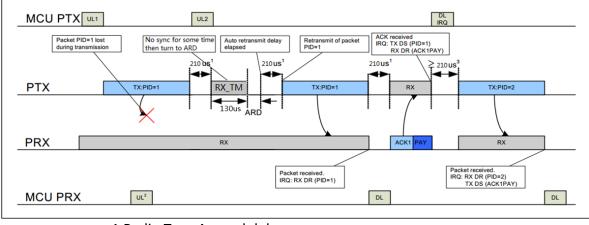

|   |      | 3.3.8  | Protocol engine transaction diagram                                                      |     |

|   | 3.4  | Dat    | ta and control interface                                                                 | 120 |

|          | 3.4.1    | Features                      | 121 |

|----------|----------|-------------------------------|-----|

|          | 3.4.2    | Functional description        | 121 |

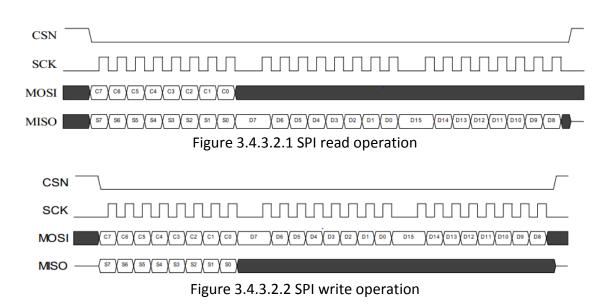

|          | 3.4.3    | SPI operation                 | 121 |

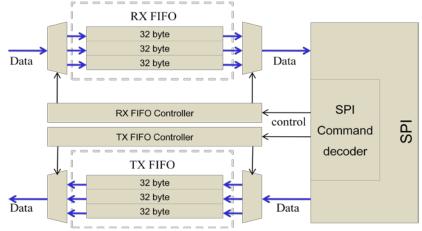

|          | 3.4.4    | Data FIFO                     | 123 |

|          | 3.4.5    | Interrupt                     | 124 |

| 3.5      | Re       | gister map                    | 125 |

|          | 3.5.1    | Register map table            | 125 |

| 3.5.1.1  | CO       | NFIG (RW) Address: 00h        | 125 |

| 3.5.1.2  | EN       | _AA (RW) Address: 01h         | 125 |

| 3.5.1.3  | EN       | _RXADDR (RW) Address: 02h     | 126 |

| 3.5.1.4  | SET      | UP_AW (RW) Address: 03h       | 126 |

| 3.5.1.5  | SET      | UP_RETR (RW) Address: 04h     | 127 |

| 3.5.1.6  | RF_      | _CH (RW) Address: 05h         | 127 |

| 3.5.1.7  | RF_      | _SETUP (RW) Address: 06h      | 127 |

| 3.5.1.8  | STA      | ATUS (RW) Address: 07h        | 128 |

| 3.5.1.9  | OB       | SERVE_TX (RW) Address: 08h    |     |

| 3.5.1.10 | RPI      | D Address: 09h                | 129 |

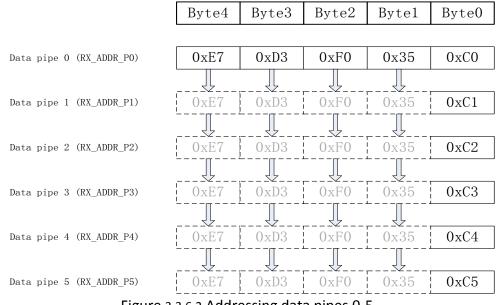

| 3.5.1.11 | RX_      | _ADDR_P0 (RW) Address: 0Ah    | 129 |

| 3.5.1.12 | -        | _ADDR_P1 (RW) Address: 0Bh    |     |

| 3.5.1.13 | RX_      | _ADDR_P2 (RW) Address: 0Ch    | 130 |

| 3.5.1.14 | -        | _ADDR_P3 (RW) Address: 0Dh    |     |

| 3.5.1.15 | RX_      | _ADDR_P4 (RW) Address: 0Eh    | 130 |

| 3.5.1.16 | -        | _ADDR_P5 (RW) Address: 0Fh    |     |

| 3.5.1.17 | _        | _ADDR(RW) Address: 10h        |     |

| 3.5.1.18 | -        | _PW_P0 (RW) Address: 11h      |     |

| 3.5.1.19 | -        | _PW_P1 (RW) Address: 12h      |     |

| 3.5.1.20 | -        | _PW_P2 (RW) Address: 13h      |     |

| 3.5.1.21 | -        | _PW_P3 (RW) Address: 14h      |     |

| 3.5.1.22 | -        | _PW_P4 (RW) Address: 15h      |     |

| 3.5.1.23 | -        | _PW_P5 (RW) Address: 16h      |     |

| 3.5.1.24 |          | O_STATUS (RW) Address: 17h    |     |

| 3.5.1.25 |          | NPD (RW) Address: 1Ch         |     |

| 3.5.1.26 |          | ATURE (RW) Address: 1Dh       |     |

| 3.5.1.27 |          | UP_VALUE (RW) Address: 1Eh    |     |

| 3.5.1.28 |          | E_GURD (RW) Address: 1Fh      |     |

| 4 Elect  |          | aracteristics                 |     |

|          | 4.1.1    | Absolute Maximum Rating       |     |

|          | 4.1.2    | DC Electrical Characteristics |     |

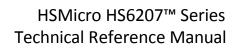

|          | 4.1.3    | AC Electrical Characteristics |     |

|          | 4.1.4    | Rf performance                |     |

|          | 4.1.5    | ypical Crystal                |     |

|          | 4.1.6    | Analog to digital conversion  |     |

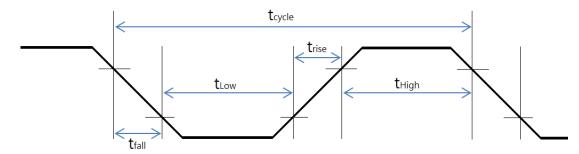

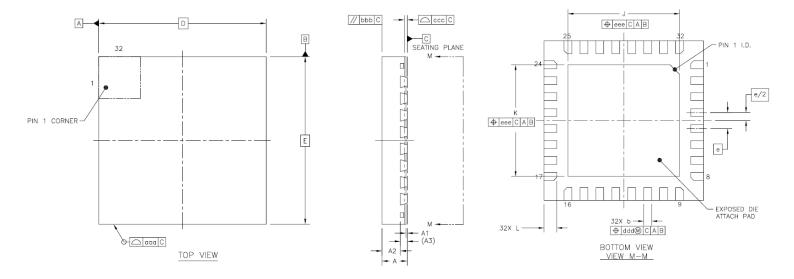

| 5 Pack   | age Info | prmation                      | 141 |

## 1 HS6207

The HS6207 is a member of the low-cost, high-performance family of intelligent 2.4 GHz RF transceivers with 32bit embedded microcontrollers. The HS6207 is optimized to provide a single chip solution for Ultra Low Power (ULP) wireless applications. The combination of processing power, memory, low power oscillators, real-time counter, and a range of power saving modes provides an ideal platform for implementation of RF protocols.

Benefits of using HS6207 include tighter protocol timing, security, lower power consumption and improved co-existence performance. For the application layer the HS6207 offers a rich set of peripherals including: I2C, UART, PWM, ADC and so on.

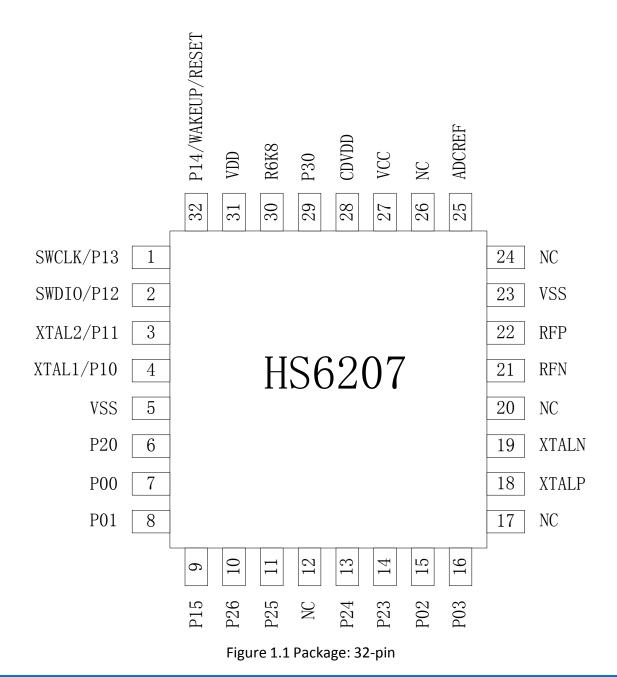

## 1.1 Pin Configuration

Rev: v1.1

## 1.2 Pin Description

## 1.2.1 **I/O Function**

| Pi | n number      |     |      |      | Func | tion Sy | mbol     |      |       |

|----|---------------|-----|------|------|------|---------|----------|------|-------|

| 32 | Configuration | 0   | 1    | 2    | 3    | 4       | 5        | 6    | 7     |

| 1  | SWD_CLK       | P13 | RXD0 | TXD1 | RXD2 | SDA     | SSP_MISO | CTS1 | PWM2B |

| 2  | SWD_DAT       | P12 | TXD0 | RXD1 | TXD2 | SCL     | SSP_SS   | RTS0 | PWM2A |

| 3  | XTAL2         | P11 | RXD0 | TXD1 | RXD2 | SDA     | SSP_CLK  | CTS0 | PWM3B |

| 4  | XTAL1         | P10 | TXD0 | RXD1 | TXD2 | SCL     | SSP_MOSI | RTS1 | PWM3A |

| 5  | VSS           |     |      |      |      |         |          |      |       |

| 6  | SWD_CLK       | P20 | RXD0 | TXD1 | RXD2 | SDA     | SSP_MISO | CTS1 | PWM1A |

| 7  | SWD_DAT       | P00 | TXD0 | RXD1 | TXD2 | SCL     | SSP_SS   | RTS0 | PWM0A |

| 8  | SWD_CLK       | P01 | RXD0 | TXD1 | RXD2 | SDA     | SSP_CLK  | CTS0 | PWM0B |

| 9  | SWD_DAT       | P15 | TXD0 | RXD1 | TXD2 | SCL     | SSP_MOSI | RTS1 | PWM1B |

| 10 | SWD_CLK       | P26 | RXD0 | TXD1 | RXD2 | SDA     | SSP_MISO | CTS1 | PWM2B |

| 11 | SWD_DAT       | P25 | TXD0 | RXD1 | TXD2 | SCL     | SSP_SS   | RTS0 | PWM2A |

| 12 | NC            |     |      |      |      |         |          |      |       |

| 13 | SWD_DAT       | P24 | RXD0 | TXD1 | RXD2 | SDA     | SSP_CLK  | CTS2 | PWM3A |

| 14 | SWD_CLK       | P23 | TXD0 | RXD1 | TXD2 | SCL     | SSP_MOSI | RTS2 | PWM3B |

| 15 | SWD_DAT       | P02 | RXD0 | TXD1 | RXD2 | SDA     | SSP_MISO | CTS2 | ADC0  |

| 16 | SWD_CLK       | P03 | TXD0 | RXD1 | TXD2 | SCL     | SSP_SS   | RTS2 | ADC1  |

| 17 | NC            |     |      |      |      |         |          |      |       |

| 18 | XTALP         |     |      |      |      |         |          |      |       |

| 19 | XTALN         |     |      |      |      |         |          |      |       |

| 20 | NC            |     |      |      |      |         |          |      |       |

| 21 | RFN           |     |      |      |      |         |          |      |       |

| 22 | RFP           |     |      |      |      |         |          |      |       |

| 23 | VSS           |     |      |      |      |         |          |      |       |

| 24 | NC            |     |      |      |      |         |          |      |       |

| 25 | ADCREF        |     |      |      |      |         |          |      |       |

| 26 | NC            |     |      |      |      |         |          |      |       |

| 27 | VCC           |     |      |      |      |         |          |      |       |

| 28 | CDVDD         |     |      |      |      |         |          |      |       |

| 29 | SWD_CLK       | P30 | TXD0 | RXD1 | TXD2 | SCL     | SSP_SS   | RTS2 | PWM0A |

| 30 | R6K8          |     |      |      |      |         |          |      |       |

| 31 | VDD           |     |      |      |      |         |          |      |       |

| 32 | Reset/Wakeup  | P14 | TXD0 | RXD1 | TXD2 | SCL     | SSP_MOSI | RTS1 | PWM1A |

Table1.2.1 I/O Description

## 1.2.2 Function Description

| Function Symbol | Description                                              |

|-----------------|----------------------------------------------------------|

| PWMxA           | PWM Group x channel A pin.                               |

| PWMxB           | PWM Group x channel B pin.                               |

| TXDx            | UART x transmit data pin.                                |

| RXDx            | UART x receive data pin.                                 |

| CTSx            | Clear to Send input pin for UART x.                      |

| RTSx            | Request to Send output pin for UART x.                   |

| SCL             | IIC interface clock pin.                                 |

| SDA             | IIC interface data pin.                                  |

| SSP_CLK         | SSP interface. (SSP clock pin)                           |

| SSP_MISO        | SSP interface. (Mast - In - Slave - Out)                 |

| SSP_MOSI        | SSP interface. (Mast - Out - Slave - In)                 |

| SSP_SS          | SSP interface. (SSP slave select pin)                    |

| ADCx            | 12-bit SAR ADC channel x input pin.                      |

| XTALP           | Crystal Pin p for RF                                     |

| XTALN           | Crystal Pin n for RF                                     |

| XTAL2           | Crystal Pin 2 for M0                                     |

| XTAL1           | Crystal Pin 1 for M0                                     |

| RFN             | Antenna interface 1                                      |

| RFP             | Antenna interface 2                                      |

| VSS             |                                                          |

| ADCREF          | Reference voltage. Connect a 100nFcapacitor to ground.   |

| NC              |                                                          |

| VCC             |                                                          |

| CDVDD           | Internal digital supply output for de-coupling purposes. |

| R6K8            |                                                          |

| VDD             |                                                          |

#### Table 1.2.2 Function Description

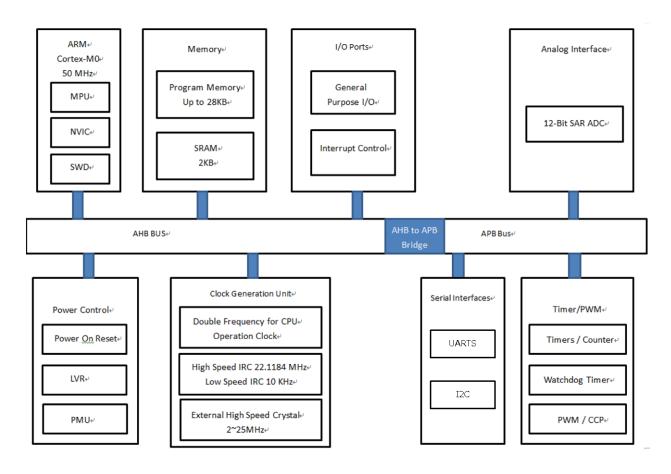

## 2 MCU

## 2.1 General Description

The HSMicro HS6207 series are low-cost 32-bit microcontroller with embedded ARM<sup>®</sup> Cortex<sup>™</sup>-M0 core for industrial control and applications which need high performance, high-integration low cost requirements.

The HSMicro HS6207 series can run up to 25MHz. The HSMicro HS6207 series provides 28Kbytes embedded program flash, flexibility data flash (Shared with program flash) and fixed 3Kbytes boot code address for the ISP and 2Kbytes embedded SRAM.

Many system level peripheral functions, such as GPIO ports, Timer, UART, SSP, IIC, PWM, Watchdog Timer, 12-bits SAR ADC and low voltage detector, have been incorporated into the HSMicro HS6207 series. The useful functions make the HSMicro HS6207 series powerful for a wide range of applications.

Additionally, the HSMicro HS6207 series is equipped with ISP (In-System Programming) and ICP (In-Circuit Programming) functions, which allow the user to update the embedded program and data flash without removing the chip from the actual end product.

## 2.2 Feature

## > Core

- ARM<sup>®</sup> Cortex<sup>™</sup>-M0 core runs up to 25MHz

- Built-in Nested Vectored Interrupt Controller (NVIC)

- Built-in 24-bit system tick timer

- A single-cycle 32-bit hardware multiplier

- Supports Serial Wire Debug (SWD) interface and 2 watchpoints / 4 breakpoints

## > Memory

- Embedded Flash memory

- ✓ 28Kbytes on-chip flash memory

- ✓ Flexibility data flash

- Fixed 3 Kbytes boot memory map for ISP application

- ✓ Minimum 100,000 program/erase cycles

- Minimum 10 years data retention

- 2KByte on-chip SRAM.

## Clock Control

- Programmable system clock source.

- External crystal input (up to 25Mhz)

- Internal 22.1184MHz high speed oscillator (+-2% @ 25°C)

- Internal 10KHz low speed oscillator

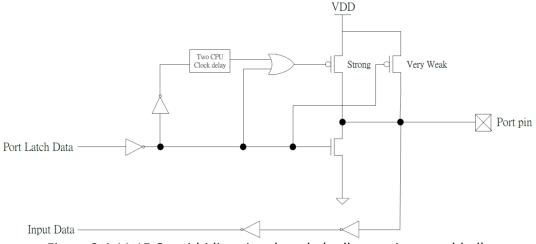

## ≻ I/O Port

- Up to 25 general-purpose I/O(GPIO) pins

- I/O pin configuration:

- ✓ Quasi-bidirectional (Pull-up Enable)

- ✓ Push-Pull (Output)

- ✓ Open drain (Pull-up Disable)

- Input only (High-impedance)

- ✓ Analog input for ADC

- I/O pin can be configured as interrupt source with edge/level setting

- High ESD: over 8KV

## > Timer

Provides two channel 32/16 bits timer

- Independent clock source for each timer

- Selectable One-shot mode, Periodic timer mode or Free-running mode

## Watchdog Timer

- clock source is internal 10KHz

- 32-bit free running counter

- Selectable timer-out interval

## Capture/ PWM

- Built-in four 16-bit PWM generators

- 8-channels PWM output

- Clock divider for four PWM generator

- Support 16-bit digital Capture mode with rising/falling/rising to falling/falling to rising capture input

- > UART

- Three sets UART interface

- Compatible with industry-standard 16C450 and 16550A UARTs

- Programmable baud-rate generator

- Internal 16 Bytes TXFIFO, 16 Bytes RXFIFO

- IrDA modulation/Demodulation

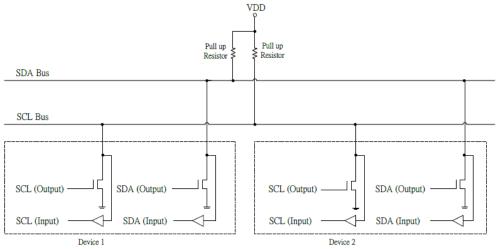

## > I2C

- One I2C interface

- Supports master/slave mode

- Support 7-bit/10-bit addressing

- Support Multi-master

- Programmable clocks allow versatile rate control

- Supports Fast-mode Plus (up to 1 Mbit/s),

Fast-mode (up to 400 Kbit/s) and

Standard-mode (up to 100 Kbit/s)

- > ADC

- 12-bit SAR ADC with 200ksps

- Up to 8 channel single-ended input.

- Supports single mode/continuous scan mode

- Each channel with an individual result registers

- Flash Memory Controller (FMC)

## 2.3 Block Diagram

- Build-in internal Flash controller for

In-Application-Programming (IAP)

- Power Management Unit

- Support Deep Power down mode

- Support Low speed mode

- Support Sleep mode

## 2.4 Functional Description

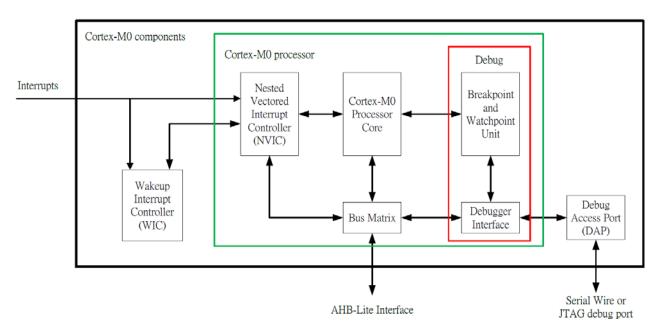

#### 2.4.1 **ARM<sup>®</sup> Cortex<sup>™</sup>-M0 core**

The CortexTM - M0 processor is a configurable, multistage, 32-bit RISC processor. It has an AMBA AHB-Lite interface and includes an NVIC component. It also has optional hardware debug functionality. The processor can execute Thumb code and is compatible with other Cortex-M profile processors. The profile supports two modes – Thread and Handler modes. Handler mode is entered as a result of an exception. An exception return can only be issued in Handler mode. Thread mode is entered on Reset, and be entered as a result of an exception return.

Figure 2.4.1 Cortex-M0 Function Block Diagram

The implemented device provides:

A low gate count processor the features:

- The ARMv6-M Thumb instruction set.

- Thumb-2 technology.

- ARMv6-M compliant 24-bit SysTick timer.

- A 32-bit hardware multiplier. (Single cycle)

- The system interface supports little-endian data accesses.

- The ability to have deterministic, fixed-latency, interrupt handing.

- C Application Binary Interface compliant exception model.

This is the ARMv6-M, C application Binary Interface(C-ABI) compliant exception model that enables

the use of pure C functions as interrupt handlers.

• Low power sleep mode entry using wait for interrupt, wait for event instructions, or the return from interrupt sleep-on-exit feature.

NVIC features:

- 32 external interrupt inputs, each with four levels of priority.

- Dedicated non-Maskable Interrupt (NMI) input.

- Support for both level-sensitive and pulse-sensitive interrupt lines.

- Wake-up Interrupt Controller (WIC), supports ultra-low power sleep mode.

Debug support:

- Four hardware breakpoints.

- Two watch points.

- Program Counter Sampling Register (PCSR) for non-intrusive code profiling.

- Single step and vector catch capabilities.

Bus interface:

- Single 32-bit AMBA-3 AHB-Lite system interface that provides simple integration to all system peripherals and memory.

- Single 32-bit slave port that supports the Debug Access Port. (DAP)

#### 2.4.2 **Memory Map**

HSMicro HS6207 series provides a 4G–byte Address space. The memory locations assigned to each on-chip modules are shown as below Table. The detailed register memory addressing and programming will be described in the following sections for individual on-chip peripherals. HSMicro HS6207 series only support little-endian data format.

|        |                        |             |     | Private peripherals                  | 0xE000_EF04 |

|--------|------------------------|-------------|-----|--------------------------------------|-------------|

|        |                        |             | ſ   | Nested Vectored Interrupt Controller | 0xE000_EF00 |

|        |                        |             |     | System Control Block                 | 0xE000_ED00 |

|        |                        |             | ·   | Nested Vectored Interrupt Controller | 0xE000 E100 |

|        |                        |             |     | SysTick system timer                 | 0xE000_E010 |

|        |                        |             | il  | System Control Block                 | 0xE000_E008 |

|        |                        |             |     | AHB peripherals                      | 0x5400_0000 |

| 4 GB   | Reserved               | OxFFFF_FFFF | i ſ | GPIO3 Control                        | 0x5380_0000 |

| 2      | Reserved               | 0xE010_0000 |     | GPIO2 Control                        | 0x5300_0000 |

|        | Private Peripheral Bus | 4           |     | GPIO1 Control                        | 0x5280_0000 |

| L      | Thvac Tempicial Dus    | 0xE000_0000 |     | GPIO0 Control                        | 0x5200_0000 |

| 2      | Reserved               | 2           |     | Reserved                             | 0x5080_0000 |

| Ĺ      | Reserved               | 0x5200_0000 |     | System Configuration                 | 0x5000_0000 |

|        | AHB peripherals        | 0x5000_0000 |     |                                      |             |

| 2      | Reserved               | < _         | ~   | APB peripherals                      | 0x4A00_0000 |

| Ĺ      | ACSCIVES.              | 0x4A00_0000 | ſ   | Flash Memory Control                 | 0x4980_0000 |

|        | APB peripherals        | <b>4</b>    | .   | Reserved                             | 0x4900_0000 |

| 1 GB   | The peripherals        | 0x4000_0000 |     | Reserved                             | 0x4880_0000 |

| <      | Reserved               | <           |     | I2C0 Control                         | 0x4800_0000 |

| Ĺ      |                        | 0x2000_0800 |     | WDT Timer Control                    | 0x4780_0000 |

| 0.5 GB | 2KB SRAM               | 0x2000_0000 |     | Reserved                             | 0x4700_0000 |

| <      | Reserved               | <           |     | Timer0/Timer1 Control                | 0x4680_0000 |

| Ĺ      |                        | 0x0000_7C00 | L   | Reserved                             | 0x4600_0000 |

| L      | 3KB ISP on-chip-flash  | 0x0000_7000 |     | UART2 Control                        | 0x4580_0000 |

| L      | 28KB on-chip- flash    | 0x0000_6000 |     | UART1 Control                        | 0x4500_0000 |

| L      | 24KB on-chip- flash    | 0x0000_5000 |     | UART0 Control                        | 0x4480_0000 |

| L      | 20KB on-chip- flash    | 0x0000_4000 |     | Reserved                             | 0x4400_0000 |

| L      | 16KB on-chip- flash    | 0x0000_3000 |     | Reserved                             | 0x4380_0000 |

|        | 12KB on-chip- flash    | 0x0000_2000 |     | ADC Control                          | 0x4300_0000 |

|        | 8KB on-chip- flash     | 0x0000_1000 |     | Capture/PWM (CCP) Control            | 0x4280_0000 |

| 0 GB   | 4KB on-chip- flash     | 0x0000_0000 | Ĺ   | Reserved                             | 0x4000_0000 |

Figure 2.4.2 Memory Map

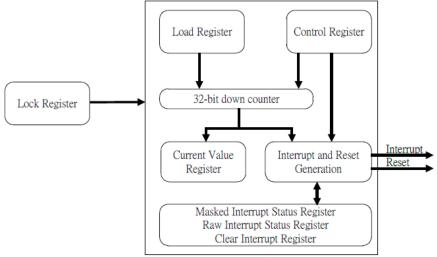

#### 2.4.3 Watchdog Timer (WDT Base address = 0x4780\_0000)

The purpose of Watchdog timer is to perform a system self-reset when system runs into an unknown state. This prevents system from hanging for an infinite period of time. Besides, Watchdog timer also supports another function to wake up from deep sleep mode.

The watchdog monitors the interrupt and asserts reset signal, when the counter reaches 0, and the counter is stop. On next enable clock edge, the counter is reloaded form the WDTLOAD Register and the countdown sequence continues. If the interrupt is not clear by the time that the counter next reached 0, then timer reasserts the reset signal.

Figure 2.4.3 Watchdog Block Diagram

| Name    | Offset | Access | Description                               | Reset value |

|---------|--------|--------|-------------------------------------------|-------------|

| WDTCON  | 0x000  | R/W    | Watchdog Control Register                 | 0x0         |

| WDTLOAD | 0x004  | R/W    | Watchdog Load Register                    | OxFFFFFFF   |

| WDTVAL  | 0x008  | RO     | Watchdog Current Value Register           | OxFFFFFFF   |

| WDTRIS  | 0x00C  | RO     | Watchdog Raw Interrupt Status Register    | 0x0         |

| WDTMIS  | 0x010  | RO     | Watchdog Masked Interrupt Status Register | 0x0         |

| WDTICLR | 0x014  | WO     | Watchdog Clear Interrupt Register         | -           |

| WDTLOCK | 0x500  | R/W    | Watchdog Lock Register                    | 0x0000000   |

Table 2.4.3 Register Overview: Watchdog Timer

## 2.4.3.1 Watchdog Control Register (WDTCON)

| Bit  | Symbol | Description                                                 | Reset |

|------|--------|-------------------------------------------------------------|-------|

|      |        |                                                             | value |

| 31:4 | -      | Reserved, should not write value to the none defined bits   | -     |

| 3:2  | WDTPRE | Watchdog Timer Pre-scale                                    | 0     |

|      |        | 0x0: Clock is divided by 1                                  |       |

|      |        | 0x1: Clock is divided by 16                                 |       |

|      |        | 0x2: Clock is divided by 256                                |       |

|      |        | 0x3: Reserved                                               |       |

| 1    | WDTRST | Enable Watchdog reset output                                | 0     |

|      |        | 0: Disable the reset                                        |       |

|      |        | 1: Enable the reset                                         |       |

| 0    | WDTIEN | Enable the interrupt. Reloads the counter from the value in | 0     |

|      |        | WDTLOAD when the interrupt is enabled, and was previously   |       |

|      |        | disabled.                                                   |       |

|      |        | 0: Disable the counter and interrupt                        |       |

|      |        | 1: Enable the counter and the interrupt                     |       |

Table 2.4.3.1 Watchdog Control Register (WDTCON)

## 2.4.3.2 Watchdog Load Register (WDTLOAD)

| Bit  | Symbol  | Description                                                    | Reset<br>value |

|------|---------|----------------------------------------------------------------|----------------|

| 31:0 | WDTLOAD | The WDTLOAD Register is a 32-bit register containing the value | OxFFFFFFFF     |

|      |         | from which the counter is to decrement. When this register is  |                |

|      |         | written to, the count is immediately restarted from the new    |                |

|      |         | value. The minimum valid value for WDTLOAD is 1                |                |

Table 2.4.3.2 Watchdog Load Register (WDTLOAD)

#### 2.4.3.3 Watchdog Current Value Register (WDTVAL)

|        |     | value                                                                        |

|--------|-----|------------------------------------------------------------------------------|

| WDTVAL |     | OxFFFFFFF                                                                    |

| WDT    | VAL | VAL The WDTVAL Register gives the current value of the decrementing counter. |

Table 2.4.3.3 Watchdog Current Value Register (WDTVAL)

#### 2.4.3.4 Watchdog Raw Interrupt Status Register (WDTRIS)

| Bit  | Symbol | Description                                               | Reset value |

|------|--------|-----------------------------------------------------------|-------------|

| 31:1 | -      | Reserved, should not write value to the none defined bits | -           |

| 0    | WDTRIS | Raw interrupt status from the counter                     | 0           |

Table 2.4.3.4 Watchdog Raw Interrupt Status Register (WDTRIS)

#### 2.4.3.5 Watchdog Masked Interrupt Status Register (WDTMIS)

| Bit  | Symbol | Description                                               | Reset value |

|------|--------|-----------------------------------------------------------|-------------|

| 31:1 | -      | Reserved, should not write value to the none defined bits | -           |

| 0    | WDTMIS | 0: Enabled interrupt status from the counter              | 0           |

|      |        | 1: Disable interrupt status from the counter              |             |

Table 2.4.3.5 Watchdog Masked Interrupt Status Register (WDTMIS)

#### 2.4.3.6 Watchdog Clear Interrupt Register (WDTICLR)

| Bit  | Symbol  | Description                                                      | Reset<br>value |

|------|---------|------------------------------------------------------------------|----------------|

| 31:0 | WDTICLR | A write of any value to the WDTICLR Register clears the watchdog | -              |

|      |         | interrupt, and reloads the counter from the value in WDTLOAD.    |                |

Table 2.4.3.6 Watchdog Clear Interrupt Register (WDTICLR)

## 2.4.3.7 Watchdog Lock Register (WDTLOCK)

| Bit  | Symbol | Description                                                       | Reset<br>value |

|------|--------|-------------------------------------------------------------------|----------------|

| 31:1 | WDTKEY | Enable write access to all other registers by writing 0x2AD5334C. | 0x0000000      |

|      |        | Disable write access by writing any other value.                  |                |

| 0    | WDTREN | Register write enable.                                            | 0              |

|      |        | 0: Write access to all other registers is disabled                |                |

|      |        | 1: Write access to all other registers is enabled                 |                |

Table 2.4.3.7 Watchdog Lock Register (WDTLOCK)

Note: Unlock by write 0x55AA6699 to WDTLOCK register.

## 2.4.4 Timer (Timer0 Base address = 0x4680\_0000; Timer1 Base address = 0x4680\_0100)

HSMicro HS6207 have two programmable 32-bits or 16bits down counter timers, user can easily implement timer control for application. The below modes are available in operation.

Free running mode: The counter wraps after reaching its zero value, and continues to count down from maximum value. The free running mode is default mode.

Periodic timer mode: The counter generates an interrupt at a constant interval, reloading the original value after wrapping past zero.

One-shot timer mode: The counter generates an interrupt once. When the counter reaches 0, it halts until you reprogram it. User can achieve this by either clearing the one-shot count bit in control register, in other case the count proceeds according to the selection of free running or periodic mode or writing new value to the Load value register.

| Name         | Offset | Access | Description                            | Reset value |

|--------------|--------|--------|----------------------------------------|-------------|

| TIMERxCON    | 0x000  | R/W    | Timer Control Register                 | 0x20        |

| TIMERxLOAD   | 0x004  | R/W    | Timer Load Register                    | 0x0000000   |

| TIMERxVAL    | 0x008  | RO     | Timer Current Value Register           | OxFFFFFFF   |

| TIMERxRIS    | 0x00C  | RO     | Timer Raw Interrupt Status Register    | 0x0         |

| TIMERxMIS    | 0x010  | RO     | Timer Masked Interrupt Status Register | 0x0         |

| TIMERxICLR   | 0x014  | WO     | Timer Clear Interrupt Register         | -           |

| TIMERxBGLOAD | 0x018  | R/W    | Timer Background Load Register         | 0x0000000   |

Table 2.4.4 Register Overview: Timer

## 2.4.4.1 Timer Control Register (TIMERxCON)

| Bit  | Symbol | Description                                               | Reset value |

|------|--------|-----------------------------------------------------------|-------------|

| 31:8 | -      | Reserved, should not write value to the none defined bits | -           |

| 7    | TMREN  | Timer Enable                                              | 0           |

|      |        | 0: Timer disabled                                         |             |

|      |        | 1: Timer enabled                                          |             |

| 6    | TMRMS  | Timer Mode Select                                         | 0           |

|      |        | 0: Timer is in free-running mode                          |             |

|      |        | 1: Timer is in periodic mode                              |             |

| 5    | TMRIE  | Interrupt Enable                                          | 1           |

|      |        | 0: Timer Interrupt disabled                               |             |

|      |        | 1: Timer Interrupt enabled                                |             |

| 4   | -      | Reserved                                  | - |

|-----|--------|-------------------------------------------|---|

|     |        |                                           |   |

| 3:2 | TMRPRE | Timer Prescale                            | 0 |

|     |        | 00: Clock is divided by 1                 |   |

|     |        | 01: Clock is divided by 16                |   |

| 1   | TMRSZ  | Selects 16/32 bit counter operation       | 0 |

|     |        | 0: 16-bit counter                         |   |

|     |        | 1: 32-bit counter                         |   |

| 0   | TMROS  | Selects one-shot or wrapping counter mode | 0 |

|     |        | 0: wrapping mode                          |   |

|     |        | 1: one-shot mode                          |   |

Table 2.4.4.1 Timer Control Register (TIMERxCON)

## 2.4.4.2 Timer Load Register (TIMERxLOAD)

| Bit  | Symbol   | Description                                                     | Reset value |

|------|----------|-----------------------------------------------------------------|-------------|

| 31:0 | TMRxLOAD | When this register is written to directly, the current count is | 0x00000000  |

|      |          | immediately reset to the new value at the next rising edge of   |             |

|      |          | TIMER CLK that is enabled by TIMER CLK enable.                  |             |

|      |          | The value in this register is also overwritten if the           |             |

|      |          | TMRXBGLOAD Register is written to, but the current count is     |             |

|      |          | not immediately affected.                                       |             |

|      |          | If values are written to both the TMRXLOAD and                  |             |

|      |          | TMRXBGLOAD Registers before an enabled rising edge on           |             |

|      |          | TIMER CLK, the following occurs:                                |             |

|      |          | 1. On the next enabled TIMER CLK edge, the value written to     |             |

|      |          | the TMRXLOAD value replaces the current count value.            |             |

|      |          | 2. Then, each time the counter reaches zero, the current        |             |

|      |          | count value is reset to the value written to TMRXBGLOAD.        |             |

|      |          | Reading from the TMRXLOAD Register at any time after the        |             |

|      |          | two writes have occurred retrieves the value written to         |             |

|      |          | TMRXBGLOAD. That is, the value read from TMRXLOAD is            |             |

|      |          | always the value that takes effect for Periodic mode after the  |             |

|      |          | next time the counter reaches zero.                             |             |

Table 2.4.4.2 Timer Load Register (TIMERxLOAD)

Rev: v1.1

#### 2.4.4.3 Timer Current Value Register (TIMERxVAL)

| Bit  | Symbol  | Description                                                               | Reset<br>value |

|------|---------|---------------------------------------------------------------------------|----------------|

| 31:0 | TMRxVAL | The TMRXVAL Register gives the current value of the decrementing counter. | OxFFFFFFF      |

Table 2.4.4.3 Timer Current Value Register (TIMERxVAL)

#### 2.4.4.4 Timer Raw Interrupt Status Register (TIMERxRIS)

| Bit  | Symbol  | Description                                               | Reset value |

|------|---------|-----------------------------------------------------------|-------------|

| 31:1 | -       | Reserved, should not write value to the none defined bits | -           |

| 0    | TMRxRIS | Raw interrupt status from the counter                     | 0           |

Table 2.4.4.4 Timer Raw Interrupt Status Register (TIMERxRIS)

#### 2.4.4.5 Timer Masked Interrupt Status Register (TIMERxMIS)

| Bit  | Symbol  | Description                                               | Reset value |

|------|---------|-----------------------------------------------------------|-------------|

| 31:1 | -       | Reserved, should not write value to the none defined bits | -           |

| 0    | TMRxMIS | Enabled interrupt status from the counter                 | 0           |

Table 2.4.4.5 Timer Masked Interrupt Status Register (TIMERxMIS)

#### 2.4.4.6 Timer Clear Interrupt Register (TIMERxICLR)

| Bit  | Symbol   | Description                                                    | Reset<br>value |

|------|----------|----------------------------------------------------------------|----------------|

| 31:0 | TMRxICLR | Any write to the TMRXICLR Register clears the interrupt output | -              |

|      |          | from the counter.                                              |                |

Table 2.4.4.6 Timer Clear Interrupt Register (TIMERxICLR)

## 2.4.4.7 Timer Background Load Register (TIMERxBGLOAD)

| Bit  | Symbol     | Description                                                                                                                                                       | Reset value |

|------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 31:0 | TMRxBGLOAD | The TMRXBGLOAD Register is 32-bits and contains the                                                                                                               | 0x00000000  |

|      |            | value from which the counter is to decrement. This is the                                                                                                         |             |

|      |            | value used to reload the counter when Periodic mode is                                                                                                            |             |

|      |            | enabled, and the current count reaches zero.                                                                                                                      |             |

|      |            | This register provides an alternative method of accessing                                                                                                         |             |

|      |            | the TMRXLOAD Register. The difference is that writes to                                                                                                           |             |

|      |            | TMRXBGLOAD do not cause the counter to immediately<br>restart from the new value.<br>Reading from this register returns the same value returned<br>from TMRXLOAD. |             |

Table 2.4.4.7 Timer Background Load Register (TIMERxBGLOAD)

#### 2.4.5 Capture/PWM (PWM Base address = 0x4280\_0000)

HSMicro HS6207 series provide four groups for capture function. The capture function input pin channel shared with PWM output channel, each channel support capture on rising/falling edge and count from rising edge to falling edge or count from falling edge to rising edge.

Pulse-width modulation is a digital technique for varying the amount of power delivered to an electronic device. By adjusting the amount of power delivered to a motor or LED, the motor speed and LED brightness can be controlled.

| Name     | Offset | Access | Description                                | Reset value |

|----------|--------|--------|--------------------------------------------|-------------|

| PWMCON0  | 0x000  | R/W    | PWM Group 0 Control Register.              | 0x00        |

| PWMLOAD0 | 0x004  | R/W    | PWM Group 0 Load Register.                 | 0x00000     |

| PWMD0A   | 0x008  | R/W    | PWM Group 0 Channel A Data Register.       | 0x00000     |

| PWMD0B   | 0x00C  | R/W    | PWM Group 0 Channel B Data Register.       | 0x00000     |

| PWMCON1  | 0x010  | R/W    | PWM Group 1 Control Register.              | 0x00        |

| PWMLOAD1 | 0x014  | R/W    | PWM Group 1 Load Register.                 | 0x00000     |

| PWMD1A   | 0x018  | R/W    | PWM Group 1 Channel A Data Register.       | 0x00000     |

| PWMD1B   | 0x01C  | R/W    | PWM Group 1 Channel B Data Register.       | 0x00000     |

| PWMCON2  | 0x020  | R/W    | PWM Group 2 Control Register.              | 0x00        |

| PWMLOAD2 | 0x024  | R/W    | PWM Group 2 Load Register.                 | 0x00000     |

| PWMD2A   | 0x028  | R/W    | PWM Group 2 Channel A Data Register.       | 0x00000     |

| PWMD2B   | 0x02C  | R/W    | PWM Group 2 Channel B Data Register.       | 0x00000     |

| PWMCON3  | 0x030  | R/W    | PWM Group 3 Control Register.              | 0x00        |

| PWMLOAD3 | 0x034  | R/W    | PWM Group 3 Load Register.                 | 0x00000     |

| PWMD3A   | 0x038  | R/W    | PWM Group 3 Channel A Data Register.       | 0x00000     |

| PWMD3B   | 0x03C  | R/W    | PWM Group 3 Channel B Data Register.       | 0x00000     |

| PWMIMSC  | 0x040  | R/W    | PWM Interrupt Mask Set and Clear Register. | 0x00        |

| PWMRIS   | 0x044  | RO     | PWM Raw Interrupt Status Register.         | 0x00        |

| PWMMIS   | 0x048  | RO     | PWM Masked Interrupt Status Register.      | 0x00        |

| PWMICLR  | 0x04C  | WO     | PWM Interrupt Clear Register.              | 0x00        |

| PWMRUN   | 0x050  | R/W    | PWM Run Register.                          | 0x0         |

Table 2.4.5 Register Overview: Capture/PWM

## 2.4.5.1 PWM Control Register (PWMCONx)

| Bit  | Symbol | Description                                               | Reset value |

|------|--------|-----------------------------------------------------------|-------------|

| 31:7 | -      | Reserved, should not write value to the none defined bits | -           |

| 6    | PWMEN  | PWM Enable                                                | 0           |

|      |        | 0: Disable                                                |             |

|      |        | 1: Enable                                                 |             |

| 5:4  | PWMPS  | PWM Prescale Select                                       | 0x0         |

|      |        | 0x0: PCLK                                                 |             |

|      |        | 0x1: PCLK / 4                                             |             |

|      |        | 0x2: PCLK / 16                                            |             |

|      |        | 0x3: PCLK / 64                                            |             |

| 3    | PWMS   | PWM Select                                                | 0           |

|      |        | 0: Capture Mode                                           |             |

|      |        | 1: PWM Mode.                                              |             |

| 2    | CHS    | Capture Channel Select                                    | 0           |

|      |        | 0: Channel A                                              |             |

|      |        | 1: Channel B                                              |             |

| 1:0  | CMS    | Capture Mode Select                                       | 0x0         |

|      |        | 0x0: Capture on rising edge                               |             |

|      |        | 0x1: Capture on falling edge                              |             |

|      |        | 0x2: Count from rising edge to falling edge               |             |

|      |        | 0x3: Count from falling edge to rising edge               |             |

Table 2.4.5.1 PWM Control Register (PWMCONx)

## 2.4.5.2 PWM Load Register (PWMLOADx)

| Bit   | Symbol  | Description                                               | Reset value |

|-------|---------|-----------------------------------------------------------|-------------|

| 31:17 | -       | Reserved, should not write value to the none defined bits | -           |

| 16    | RELOAD  | PWM Reload Enable                                         | 0           |

|       |         | When RELOAD = '0', Reload Value = 0xFFFF                  |             |

|       |         | When RELOAD = '1', Reload Value = PWMLOAD                 |             |

| 15:0  | PWMLOAD | PWM Load Value                                            | 0x0000      |

Table 2.4.5.2 PWM Load Register (PWMLOADx)

## 2.4.5.3 PWM Data Register (PWMDxA/PWMDxB)

| Bit   | Symbol | Description                                               | Reset value |

|-------|--------|-----------------------------------------------------------|-------------|

| 31:17 | -      | Reserved, should not write value to the none defined bits | -           |

|       |        |                                                           |             |

| 16   | PWMOP   | PWM Output Polarity Select.<br>When PWMOP = '0', PWM leading low output.<br>When PWMOP = '1', PWM leading high output. | 0      |

|------|---------|------------------------------------------------------------------------------------------------------------------------|--------|

| 15:0 | PWMDATA | PWM Data                                                                                                               | 0x0000 |

Table 2.4.5.3 PWM Data Register (PWMDxA/PWMDxB)

#### 2.4.5.4 PWM Interrupt Mask Set and Clear Register (PWMIMSC)

| Bit  | Symbol   | Description                                               | Reset |

|------|----------|-----------------------------------------------------------|-------|

|      |          |                                                           | value |

| 31:8 | -        | Reserved, should not write value to the none defined bits | -     |

| 7    | PWMIMSC7 | PWM Group 3 Overflow Interrupt Mask Set and Clear.        | 0     |

|      |          | 0: Disable                                                |       |

|      |          | 1: Enable                                                 |       |

| 6    | PWMIMSC6 | PWM Group 2 Overflow Interrupt Mask Set and Clear.        | 0     |

|      |          | 0: Disable                                                |       |

|      |          | 1: Enable                                                 |       |

| 5    | PWMIMSC5 | PWM Group 1 Overflow Interrupt Mask Set and Clear.        | 0     |

|      |          | 0: Disable                                                |       |

|      |          | 1: Enable                                                 |       |

| 4    | PWMIMSC4 | PWM Group 0 Overflow Interrupt Mask Set and Clear.        | 0     |

|      |          | 0: Disable                                                |       |

|      |          | 1: Enable                                                 |       |

| 3    | PWMIMSC3 | PWM Group 3 Compare/Capture Interrupt Mask Set and        | 0     |

|      |          | Clear.                                                    |       |

|      |          | 0: Disable                                                |       |

|      |          | 1: Enable                                                 |       |

| 2    | PWMIMSC2 | PWM Group 2 Compare/Capture Interrupt Mask Set and        | 0     |

|      |          | Clear.                                                    |       |

|      |          | 0: Disable                                                |       |

|      |          | 1: Enable                                                 |       |

| 1    | PWMIMSC1 | PWM Group 1 Compare/Capture Interrupt Mask Set and        | 0     |

|      |          | Clear.                                                    |       |

|      |          | 0: Disable                                                |       |

|      |          | 1: Enable                                                 |       |

| 0    | PWMIMSC0 | PWM Group 0 Compare/Capture Interrupt Mask Set and        | 0     |

|      |          | Clear.                                                    |       |

|      |          | 0: Disable                                                |       |

|      |          | 1: Enable                                                 |       |

Table 2.4.5.4 PWM Interrupt Enable Register (PWMIMSC)

## 2.4.5.5 PWM Raw Interrupt Status Register (PWMRIS)

| Bit  | Symbol  | Description                                               | Reset value |

|------|---------|-----------------------------------------------------------|-------------|

| 31:8 | -       | Reserved, should not write value to the none defined bits | -           |

| 7    | PWMRIS7 | PWM Group 3 Raw Overflow Interrupt Status                 | 0           |

| 6    | PWMRIS6 | PWM Group 2 Raw Overflow Interrupt Status                 | 0           |

| 5    | PWMRIS5 | PWM Group 1 Raw Overflow Interrupt Status                 | 0           |

| 4    | PWMRIS4 | PWM Group 0 Raw Overflow Interrupt Status                 | 0           |

| 3    | PWMRIS3 | PWM Group 3 Raw Compare/Capture Interrupt Status          | 0           |

| 2    | PWMRIS2 | PWM Group 2 Raw Compare/Capture Interrupt Status          | 0           |

| 1    | PWMRIS1 | PWM Group 1 Raw Compare/Capture Interrupt Status          | 0           |

| 0    | PWMRIS0 | PWM Group 0 Raw Compare/Capture Interrupt Status          | 0           |

Table 2.4.5.5 PWM Raw Interrupt Status Register (PWMRIS)

#### 2.4.5.6 PWM Masked Interrupt Status Register (PWMMIS)

| Bit  | Symbol         | Description                                               | Reset value |

|------|----------------|-----------------------------------------------------------|-------------|

| 31:8 | -              | Reserved, should not write value to the none defined bits | -           |

| 7    | PWMMIS7        | PWM Group 3 Masked Overflow Interrupt Status              | 0           |

| 6    | PWMMIS6        | PWM Group 2 Masked Overflow Interrupt Status              | 0           |

| 5    | PWMMIS5        | PWM Group 1 Masked Overflow Interrupt Status              | 0           |

| 4    | PWMMIS4        | PWM Group 0 Masked Overflow Interrupt Status              | 0           |

| 3    | PWMMIS3        | PWM Group 3 Masked Compare/Capture Interrupt Status       | 0           |

| 2    | PWMMIS2        | PWM Group 2 Masked Compare/Capture Interrupt Status       | 0           |

| 1    | PWMMIS1        | PWM Group 1 Masked Compare/Capture Interrupt Status       | 0           |

| 0    | <b>PWMMIS0</b> | PWM Group 0 Masked Compare/Capture Interrupt Status       | 0           |

Table 2.4.5.6 PWM Masked Interrupt Status Register (PWMMIS)

#### 2.4.5.7 PWM Interrupt Clear Register (PWMICLR)

| Bit  | Symbol   | Description                                                   | Reset |

|------|----------|---------------------------------------------------------------|-------|

|      |          |                                                               | value |

| 31:8 | -        | Reserved, should not write value to the none defined bits     | -     |

| 7    | PWMICLR3 | Writing "1" to this bit clears PWM Group 3 Overflow Interrupt | 0     |

|      |          | Status                                                        |       |

| 6    | PWMICLR2 | Writing "1" to this bit clears PWM Group 2 Overflow Interrupt | 0     |

|      |          | Status                                                        |       |

| 5 | PWMICLR1 | Writing "1" to this bit clears PWM Group 1 Overflow Interrupt<br>Status        | 0 |

|---|----------|--------------------------------------------------------------------------------|---|

| 4 | PWMICLR0 | Writing "1" to this bit clears PWM Group 0 Overflow Interrupt<br>Status        | 0 |

| 3 | PWMICLR3 | Writing "1" to this bit clears PWM Group 3 Compare/Capture<br>Interrupt Status | 0 |

| 2 | PWMICLR2 | Writing "1" to this bit clears PWM Group 2 Compare/Capture<br>Interrupt Status | 0 |

| 1 | PWMICLR1 | Writing "1" to this bit clears PWM Group 1 Compare/Capture<br>Interrupt Status | 0 |

| 0 | PWMICLR0 | Writing "1" to this bit clears PWM Group 0 Compare/Capture<br>Interrupt Status | 0 |

Table 2.4.5.7 PWM Interrupt Clear Register (PWMICLR)

#### 2.4.5.8 PWM Run Register (PWMRUN)

| Bit  | Symbol  | Description                                               | Reset value |

|------|---------|-----------------------------------------------------------|-------------|

| 31:4 | -       | Reserved, should not write value to the none defined bits | -           |

| 3    | PWMRUN3 | PWM Group 3 Run.                                          | 0           |

|      |         | 0: Stop                                                   |             |

|      |         | 1: Run                                                    |             |

| 2    | PWMRUN2 | PWM Group 2 Run.                                          | 0           |

|      |         | 0: Stop                                                   |             |

|      |         | 1: Run                                                    |             |

| 1    | PWMRUN1 | PWM Group 1 Run.                                          | 0           |

|      |         | 0: Stop                                                   |             |

|      |         | 1: Run                                                    |             |

| 0    | PWMRUN0 | PWM Group 0 Run.                                          | 0           |

|      |         | 0: Stop                                                   |             |

|      |         | 1: Run                                                    |             |

Table 2.4.5.8 PWM Run Register (PWMRUN)

#### 2.4.6 Universal Asynchronous Receiver/Transmitter (UART) with modem control (UART0 Base address = 0x4480\_0000; UART1 Base address = 0x4500\_0000; UART2 Base address = 0x4580\_0000)

HSMicro HS6207 series provides three set universal asynchronous receiver/transmitter (UART). UART performs normal speed UART and support flow control function.

The UART baud rate is calculated as: Baud Rate = PCLK / (16 x DLR)

| Name       | Offset | Access | Description                                                          | Reset  |

|------------|--------|--------|----------------------------------------------------------------------|--------|

|            |        |        |                                                                      | value  |

| UARTxRBR   | 0x000  | RO     | Receiver Buffer Register. Contains the next received character to    | -      |

|            |        |        | be read.                                                             |        |

| UARTxTHR   | 0x004  | WO     | Transmit Holding Register. The next character to be transmitted      | -      |

|            |        |        | is written here.                                                     |        |

| UARTxDLR   | 0x008  | R/W    | Divisor Latch Register. The full divisor is used to generate a baud  | 0x0001 |

|            |        |        | rate from the fractional rate divider.                               |        |

| UARTxIER   | 0x00C  | R/W    | Interrupt Enable Register. Contains individual interrupt enable      | 0x00   |

|            |        |        | bits for the 7 potential UART interrupts.                            |        |

| UARTxIIR   | 0x010  | RO     | Interrupt Identification Register. Identifies which interrupt(s) are | 0x01   |

|            |        |        | pending.                                                             |        |

| UARTxFCR   | 0x014  | WO     | FIFO Control Register. Controls UART FIFO usage and modes.           | 0x00   |

| UARTxLCR   | 0x018  | R/W    | Line Control Register. Contains controls for frame formatting and    | 0x00   |

|            |        |        | break generation.                                                    |        |

| UARTxMCR   | 0x01C  | R/W    | Modem control register                                               | 0x00   |

| UARTxLSR   | 0x020  | RO     | Line Status Register. Contains flags for transmit and receive        | 0x60   |

|            |        |        | status, including line errors.                                       |        |

| UARTxMSR   | 0x024  | RO     | Modem status register                                                | 0x00   |

| UARTxSCR   | 0x028  | R/W    | Scratch Pad Register. Eight-bit temporary storage for software.      | 0x00   |

| UARTxEFR   | 0x02C  | R/W    | Enhanced Features Register                                           | 0x00   |

| UARTxXON1  | 0x030  | R/W    | XON1 Register                                                        | 0x00   |

| UARTxXON2  | 0x034  | R/W    | XON2 Register                                                        | 0x00   |

| UARTxXOFF1 | 0x038  | R/W    | XOFF1 Register                                                       | 0x00   |

| UARTxXOFF2 | 0x03C  | R/W    | XOFF2 Register                                                       | 0x00   |

Table 2.4.6 Register Overview: Universal Asynchronous Receiver/Transmitter (UART)

Rev: v1.1

## 2.4.6.1 UART Receiver Buffer Register (UARTxRBR)

| Bit  | Symbol | Description                                                                              | Reset<br>value |

|------|--------|------------------------------------------------------------------------------------------|----------------|

| 31:8 | -      | Reserved, should not write value to the none defined bits                                | -              |

| 7:0  | RBR    | The UART Receiver Buffer Register contains the oldest received byte in the UART RX FIFO. | -              |

Table 2.4.6.1 UART Receiver Buffer Register (UARTxRBR)

## 2.4.6.2 UART Transmitter Holding Register (UARTxTHR)

| Bit  | Symbol | Description                                                         | Reset<br>value |

|------|--------|---------------------------------------------------------------------|----------------|

| 31:8 | -      | Reserved, should not write value to the none defined bits           | -              |

| 7:0  | THR    | Writing to the UART Transmit Holding Register causes the data to be | -              |

|      |        | stored in the UART transmit FIFO. The byte will be sent when it     |                |

|      |        | reaches the bottom of the FIFO and the transmitter is available.    |                |

Table 2.4.6.2 UART Transmitter Holding Register (UARTxTHR)

## 2.4.6.3 UART Divisor Latch Register (UARTxDLR)

| Bit   | Symbol | Description                                                         | Reset  |

|-------|--------|---------------------------------------------------------------------|--------|

|       |        |                                                                     | value  |

| 31:16 | -      | Reserved, should not write value to the none defined bits           | -      |

| 15:0  | DLR    | Divisor Latch Register. The full divisor is used to generate a baud | 0x0001 |

|       |        | rate from the fractional rate divider.                              |        |

|       |        | Baud rate = PCLK / 16×DLR                                           |        |

Table 2.4.6.3 UART Divisor Latch Register (UARTxDLR)

#### 2.4.6.4 UART Interrupt Enable Register (UARTxIER)

| Bit     | Symbol | Description                                               | Reset<br>value |

|---------|--------|-----------------------------------------------------------|----------------|

| 31<br>8 | -      | Reserved, should not write value to the none defined bits | -              |

| 7 | CTSIE  | CTS Interrupt Enable, Enable a rising edge is detected on the CTS                     | 0 |

|---|--------|---------------------------------------------------------------------------------------|---|

| / | CISIE  | CTS Interrupt Enable. Enable a rising edge is detected on the CTS modem control line. | 0 |

|   |        |                                                                                       |   |

|   |        | 0: Disable the CTS interrupt.                                                         |   |

| 6 | DTCLE  | 1: Enable the CTS interrupt.                                                          | 0 |

| 6 | RTSIE  | RTS Interrupt Enable. Enable a rising edge is detected on the RTS                     | 0 |

|   |        | modem control line.                                                                   |   |

|   |        | 0: Disable the RTS interrupt.                                                         |   |

|   |        | 1: Enable the RTS interrupt.                                                          |   |

| 5 | XOFIE  | XOFF Interrupt Enable. Enable an XOFF character is received.                          | 0 |

|   |        | 0: Disable the XOF interrupt.                                                         |   |

|   |        | 1: Enable the XOF interrupt.                                                          |   |

|   |        |                                                                                       |   |

| 4 | -      | Reserved, should not write value to the none defined bits                             | - |

|   |        |                                                                                       |   |

|   |        |                                                                                       |   |

|   |        |                                                                                       |   |

| 3 | MDSIE  | Modem Status Interrupt Enable.                                                        | 0 |

|   |        | 0: Disable the modem status interrupts.                                               |   |

|   |        | 1: Enable the modem status interrupts.                                                |   |

|   |        |                                                                                       |   |

| 2 | RLSIE  | RX Line Status Interrupt Enable. Enables the UART RX line status                      | 0 |

|   |        | interrupts. The status of this interrupt can be read from LSR[4:1].                   |   |

|   |        | 0: Disable the RX line status interrupts.                                             |   |

|   |        | 1: Enable the RX line status interrupts.                                              |   |

| 1 | THREIE | TX Holding Register Empty Interrupt Enable. Enables the THREIE                        | 0 |

|   |        | interrupt for UART. The status of this interrupt can be read from                     |   |

|   |        | LSR[5].                                                                               |   |

|   |        | 0: Disable the THREIE interrupts.                                                     |   |

| 0 | RBRIE  | RX Buffer Register Interrupt Enable. Enables the Receive Data                         | 0 |

|   |        | Available interrupt for UART. It also controls the Character Receive                  |   |

|   |        | Time-out interrupt.                                                                   |   |

|   |        | 0: Disable the RBRIE interrupts.                                                      |   |

| L |        |                                                                                       |   |

Table 2.4.6.4 UART Interrupt Enable Register (UARTxIER)

## 2.4.6.5 UART Interrupt Identification Register (UARTxIIR)

| Bit  | Symbol | Description                                               | Reset<br>value |

|------|--------|-----------------------------------------------------------|----------------|

| 31:6 | -      | Reserved, should not write value to the none defined bits | -              |

| 5   | INTHFC | Hardware Flow Control (CTS or RTS rising edge)                          | 0 |

|-----|--------|-------------------------------------------------------------------------|---|

|     |        | If Set ("1") indicating that an XOFF character has been received. It is |   |

|     |        | cleared by reading the Interrupt Identification Register.               |   |

| 4   | INTSFC | Software Flow Control (XOFF character received)                         | 0 |

|     |        | If Set ("1") indicating that a rising edge has been detected on either  |   |

|     |        | the RTS/CTS Modem Control line. It is cleared by reading the            |   |

|     |        | Interrupt Identification Register.                                      |   |

| 3:1 | INTID  | Interrupt identification.                                               | 0 |

|     |        | 0x3: 1 - Receive Line Status.                                           |   |

|     |        | 0x2: 2a - Receive Data Available.                                       |   |

|     |        | 0x6: 2b - Receive FIFO Character Time-out Indicator.                    |   |

|     |        | 0x1: 3 - TX Holding Register Empty.                                     |   |

|     |        | 0x0: 4 - Modem Status change.                                           |   |

| 0   | INT    | Interrupt status. Note that IIR[0] is active low. The pending interrupt | 1 |

|     | STATUS | can be determined by evaluating IIR[3:1].                               |   |

|     |        | 0: At least one interrupt is pending.                                   |   |

|     |        | 1: No interrupt is pending.                                             |   |

Table 2.4.6.5 UART Interrupt Identification Register (UARTxIIR)

## 2.4.6.6 UART FIFO Control Register (UARTxFCR)

| Bit  | Symbol   | Description                                                       | Reset |

|------|----------|-------------------------------------------------------------------|-------|

|      |          |                                                                   | value |

| 31:8 | -        | Reserved, should not write value to the none defined bits         | -     |

| 7:6  | RXTL     | RX Trigger Level. These two bits determine how many receiver UART | 0     |

|      |          | FIFO characters must be written before an interrupt is activated. |       |

|      |          | 0x0: Trigger level 0 (1 character).                               |       |

|      |          | 0x1: Trigger level 1 (4 characters).                              |       |

|      |          | 0x2: Trigger level 2 (8 characters).                              |       |

|      |          | 0x3: Trigger level 3 (14 characters).                             |       |

| 5:4  | TXTL     | TX Trigger Level. These two bits determine how many transmit UART | 0     |

|      |          | FIFO characters must be written before an interrupt is activated. |       |

|      |          | 0x0: Trigger level 0 (1 character).                               |       |

|      |          | 0x1: Trigger level 1 (4 characters).                              |       |

|      |          | 0x2: Trigger level 2 (8 characters).                              |       |

|      |          | 0x3: Trigger level 3 (14 characters).                             |       |

| 3    | Reserved | Reserved, should not write value to the none defined bits         | -     |

| 2 | TXFIFO | TX FIFO Reset                                                        | 0 |

|---|--------|----------------------------------------------------------------------|---|

|   | RST    | 0: No impact on either of UART FIFOs.                                |   |

|   |        | 1: Writing a logic 1 to FCR[2] will clear all bytes in UART TX FIFO, |   |

|   |        | reset the pointer logic. This bit is self-clearing.                  |   |

| 1 | RXFIFO | RX FIFO Reset                                                        | 0 |

|   | RST    | 0: No impact on either of UART FIFOs.                                |   |

|   |        | 1: Writing a logic 1 to FCR[1] will clear all bytes in UART RX FIFO, |   |

|   |        | reset the pointer logic. This bit is self-clearing.                  |   |

| 0 | FIFOEN | FIFO Enable                                                          | 0 |

|   |        | 0: UART FIFOs are disabled. Must not be used in the application.     |   |

|   |        | 1: Active high enable for both UART RX and TX FIFOs and FCR[7:1]     |   |

|   |        | access. This bit must be set for proper UART operation. Any          |   |

|   |        | transition on this bit will automatically clear the UART FIFOs.      |   |

Table 2.4.6.6 UART FIFO Control Register (UARTxFCR)

## 2.4.6.7 UART Line Control Register (UARTxLCR)

| Bit  | Symbol | Description                                                          | Reset |

|------|--------|----------------------------------------------------------------------|-------|

|      |        |                                                                      | value |

| 31:7 | -      | Reserved, should not write value to the none defined bits            | -     |

| 6    | BCON   | Break Control                                                        | 0     |

|      |        | 0: Disable break transmission.                                       |       |

|      |        | 1: Enable break transmission. Output pin UART TXD is forced to logic |       |

|      |        | 0 when LCR[6] is active high.                                        |       |

| 5:4  | PSEL   | Parity Select                                                        | 0     |

|      |        | 0x0: Odd parity. Number of 1s in the transmitted character and the   |       |

|      |        | attached parity bit will be odd.                                     |       |

|      |        | 0x1: Even Parity. Number of 1s in the transmitted character and the  |       |

|      |        | attached parity bit will be even.                                    |       |

|      |        | 0x2: Forced 1 stick parity.                                          |       |

|      |        | 0x3: Forced 0 stick parity.                                          |       |

| 3    | PEN    | Parity Enable                                                        | 0     |

|      |        | 0: Disable parity generation and checking.                           |       |

|      |        | 1: Enable parity generation and checking.                            |       |

| 2    | SBS    | Stop Bit Select                                                      | 0     |

|      |        | 0: 1 stop bit.                                                       |       |

|      |        | 1: 2 stop bits (1.5 if LCR[1:0]=00).                                 |       |

| 1:0  | WLS    | Word Length Select                                                   | 0     |

|      |        | 0x0: 5-bit character length.                                         |       |

|      |        | 0x1: 6-bit character length.                                         |       |

|      |        | 0x2: 7-bit character length.                                         |       |

|      |        | 0x3: 8-bit character length.                                         |       |

Table 2.4.6.7 UART Line Control Register (UARTxLCR)

## 2.4.6.8 UART Modem Control Register (UARTxMCR)

| Bit  | Symbol | Description                                                         | Reset |

|------|--------|---------------------------------------------------------------------|-------|

|      |        |                                                                     | value |

| 31:8 | -      | Reserved, should not write value to the none defined bits           | -     |

| 7    | XOFFS  | XOFF Status                                                         | 0     |

|      |        | This read-only bit is set to "1" when an XOFF character is received |       |

|      |        | and cleared when an XON character is received.                      |       |

| 6   | IREN | IrDA mode enables                                               | 0 |

|-----|------|-----------------------------------------------------------------|---|

|     |      | 0: IrDA mode on UART is disabled,                               |   |

|     |      | 1: IrDA mode on UART is enabled.                                |   |

| 5   | -    | Reserved, should not write value to the none defined bits       | - |

|     |      |                                                                 |   |

|     |      |                                                                 |   |

| 4   | MLBM | Modem Loop back mode                                            | 0 |

|     |      | 0: Disable modem loopback mode.                                 |   |

|     |      | 1: Enable modem loopback mode.                                  |   |

| 3:2 | -    | Reserved, should not write value to the none defined bits       | - |

|     |      |                                                                 |   |

|     |      |                                                                 |   |

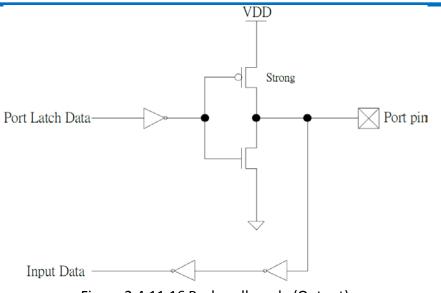

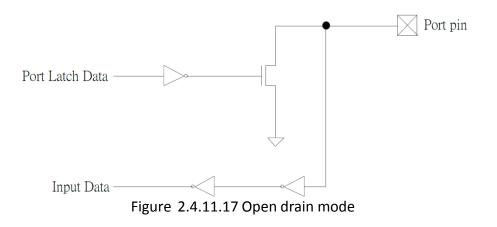

| 1   | RTS  | Source for modem output pin RTS. This bit reads as 0 when modem | 0 |